| Agenda                          |   |

|---------------------------------|---|

| 1. Motivation                   |   |

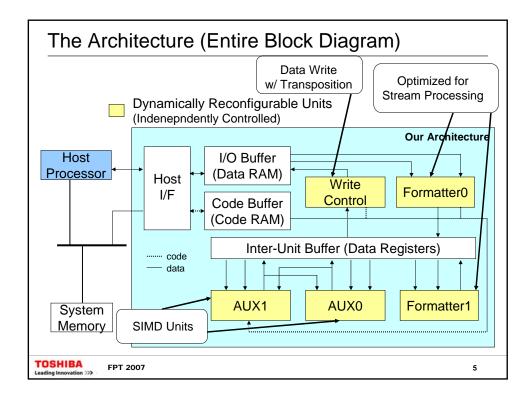

| 2. The Architecture             |   |

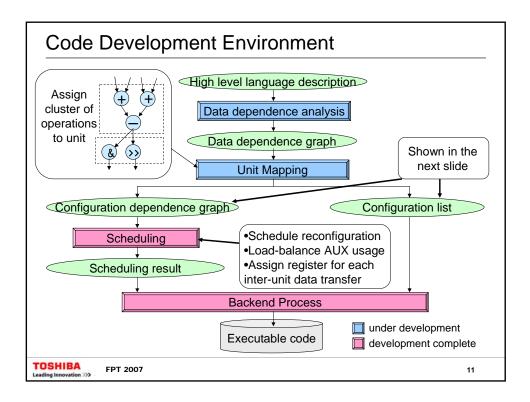

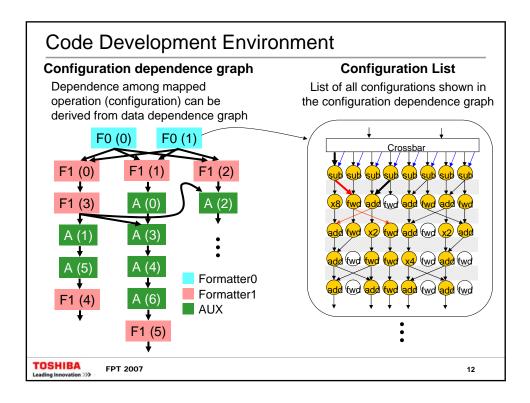

| 3. Code Development Environment |   |

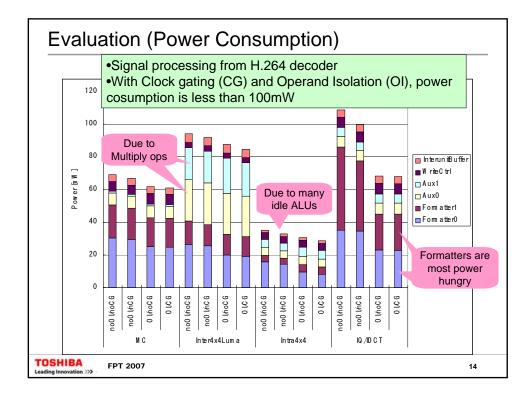

| 4. Evaluation                   |   |

| 5. Conclusion                   |   |

|                                 |   |

|                                 |   |

|                                 |   |

|                                 |   |

|                                 |   |

|                                 |   |

|                                 |   |

| TOSHIBA FPT 2007                | 2 |

| <ul> <li>Result of logic synthesis</li> <li>Logic Area includes the random logic and data register</li> <li>Memory Area includes Configuration memories &amp; Cfg<br/>Controller codes</li> <li>Memory Size doubled for double buffering</li> <li>Expected operation frequency: 300MHz</li> </ul> |                   |                    |                   |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|-------------------|--|--|--|--|--|

| Unit                                                                                                                                                                                                                                                                                              | Logic Area [gate] | Memory Area [gate] | Memory Size [bit] |  |  |  |  |  |

| Formatter0                                                                                                                                                                                                                                                                                        | 82115             | 85300              | 5584 × 2          |  |  |  |  |  |

| Formatter1                                                                                                                                                                                                                                                                                        | 78350             | 59102              | 3504 x 2          |  |  |  |  |  |

| Aux (one unit)                                                                                                                                                                                                                                                                                    | 62412 x 2         | 32164 x 2          | 2080 x 2          |  |  |  |  |  |

| WriteCtrl                                                                                                                                                                                                                                                                                         | 6535              | 43524              | 2976 x 2          |  |  |  |  |  |

| InterunitBuffer                                                                                                                                                                                                                                                                                   | 32194             | 0                  | C                 |  |  |  |  |  |

| Total                                                                                                                                                                                                                                                                                             | 326691            | 252284             | 16224             |  |  |  |  |  |

| Evaluat                                                                                         | Evaluation (Performance)                                                                               |          |                   |        |                   |      |           |  |  |  |  |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------|-------------------|--------|-------------------|------|-----------|--|--|--|--|

| Achi                                                                                            | Peformance per signal processing<br>Achieves better performance by frequently switching configurations |          |                   |        |                   |      |           |  |  |  |  |

|                                                                                                 | cycle                                                                                                  | I∕O Buf. | Form.0            | Form.1 | AUX0              | AUX1 | Wr. Ctrl. |  |  |  |  |

| MC                                                                                              | 102                                                                                                    | 82/82    | 92/5              | 64/1   | 64/1              | 0/0  | 82/3      |  |  |  |  |

| Inter4x4Lum                                                                                     | na <mark>64</mark>                                                                                     | 30/8     | 30/5              | 20/3   | 32/10             | 32/8 | 8/2       |  |  |  |  |

| Intra4x4                                                                                        | 30                                                                                                     | 4/8      | 4/2               | 4/1    | 3/2               | 3/2  | 8/2       |  |  |  |  |

| IQ/IDCT                                                                                         | 225                                                                                                    | 182/192  | 207/17            | 96/2   | 102/6             | 78/7 | 192/9     |  |  |  |  |

|                                                                                                 | # of I/O Buffer access # of configuration switches/<br>(read/write) unique configurations              |          |                   |        |                   |      |           |  |  |  |  |

| Performance of H.264 decoder (baseline profile)                                                 |                                                                                                        |          |                   |        |                   |      |           |  |  |  |  |

| By applying double buffering technique with doubled Cfg Mem, performance increased by about 70% |                                                                                                        |          |                   |        |                   |      |           |  |  |  |  |

|                                                                                                 |                                                                                                        |          | Single Cfg Mem    |        | Double Cfg Mem    |      |           |  |  |  |  |

| Q                                                                                               | CIF(176x1                                                                                              | 44)      | Up to 408 frame/s |        | Up to 683 frame/s |      |           |  |  |  |  |

| С                                                                                               | IF (352x2                                                                                              | 288)     | Up to 76 frame/s  |        | Up to 125 frame/s |      |           |  |  |  |  |

| V                                                                                               | GA (640x4                                                                                              | 180)     | Up to 37 frame/s  |        | Up to 64 frame/s  |      |           |  |  |  |  |

| OSHIBA<br>ading Innovation >>>                                                                  | РТ 2007                                                                                                |          |                   |        |                   |      | 15        |  |  |  |  |

## Conclusion

- A new dynamically reconfigurable architecture is proposed

- Optimized for stream processing by eliminating redundant resources

- Unique pipeline-style reconfiguration increases resource usage, thus increases performance

## Code development environment is partially complete

- Need to manually describe configurations and dependences among them

- Automatic code development from High level description is the goal

- RTL design done and complete evaluation with H.264 decoder

- 580Kgates (double buffer), power consumption less than 100mW, decode more than 60 VGA frame/s

- Evaluation with other application will be done after code development environment finished

TOSHIBA FPT 2007

16