Smart Base Station Antennas for New Generation Broadband Mobile Communications

The project is funded by HKSAR Innovation and Technology Commission

AchievementsIntegrated Circuit DesignPhase Lock Loop

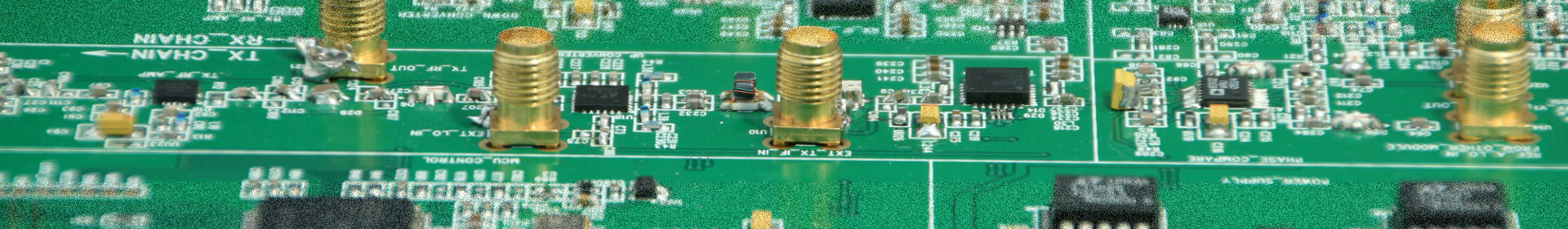

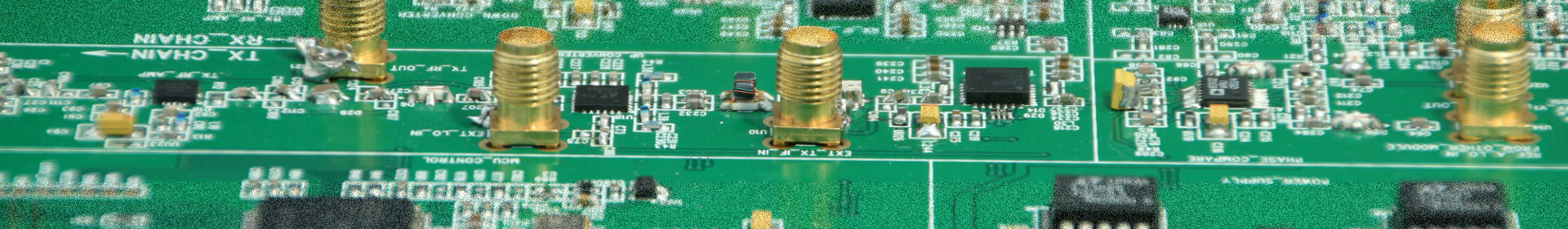

GaAs RFIC Design (1W)

CMOS RFIC Design

|

||||||||||||||||||||||||||||||||||